题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

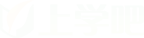

图T7.5是用两片同步十进制加/减计数器74LS190组成的加/减计数器。74LS190的功能表见表T7.5。C/B

端是进位/借位输出端。在加法计数状态下,当Q3Q2Q1Q0=1001时,C/B=1,否则为0。在减法计数状态下,当Q3Q2Q1Q0=0000时,C/B=1,否则为0。试分析在M=1和M=0两种情况下,图T7.5电路各为几进制计数器,各为加法计数器还是减法计数器,并说明在什么情况下输出Y等于1。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

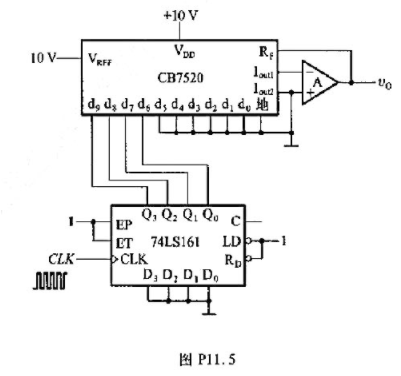

,试画出输出电压v0的波形,并标出波形图上各点电压的幅度.

,试画出输出电压v0的波形,并标出波形图上各点电压的幅度.