题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

用JK触发器设计一个同步六进制加1计数器。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“用JK触发器设计一个同步六进制加1计数器。”相关的问题

更多“用JK触发器设计一个同步六进制加1计数器。”相关的问题

第1题

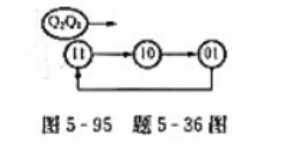

用边沿JK触发器设计一个同步三进制减法计数器,状态图如图5-95所示.试回答下列问题:

(1)最少用几个触发器?

(2)列出状态表;

(3)求出最简驱动方程:

(4)画出逻辑电路图;

(5)检查能否自启动。

第9题

为了保护您的账号安全,请在“上学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

上学吧

上学吧

微信搜一搜

微信搜一搜

上学吧

上学吧